# Московский Государственный Университет имени М. В. Ломоносова

Факультет Вычислительной Математики и Кибернетики Кафедра Автоматизации Систем Вычислительных Комплексов

НЕ ЯВЛЯЕТСЯ ОФИЦИАЛЬНЫМ УЧЕБНЫМ ПОСОБИЕМ

## Вычислительные системы

(VII семестр)

лектор — профессор А. Н. Томилин составитель — <u>a s@interwave.ru</u>

### Содержание

| Введение                                                | 3   |

|---------------------------------------------------------|-----|

| Классификация архитектур вычислительных систем          | 11  |

| Параллелизм работы основных устройств машины            | 12  |

| Параллелизм работы АЛУ                                  | 22  |

| Векторно-конвейерная ЭВМ: Стау                          | 26  |

| Модульно-конвейерный процессор (МКП)                    | 32  |

| Электроника СС БИС («Красный Крей»)                     |     |

| ILLIAC VI                                               |     |

| Многопроцессорные вычислительные комплексы              | 40  |

| MPP                                                     |     |

| Иерархия памяти                                         |     |

| Кэш (cache)                                             |     |

| Структурная организация оперативной памяти              |     |

| Сегментная организация памяти                           |     |

| Страничная организация памяти                           |     |

| Средства поддержки операционной системы                 |     |

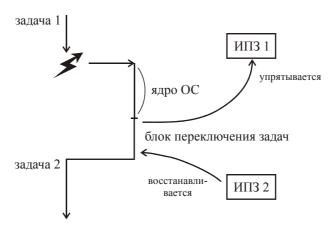

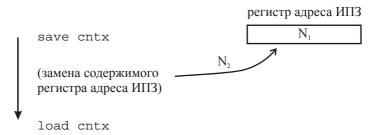

| Переключение процессов                                  |     |

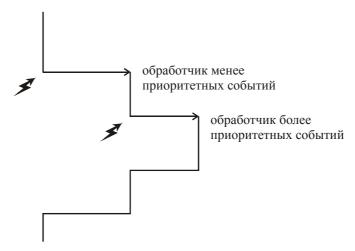

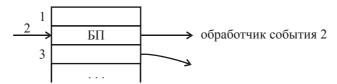

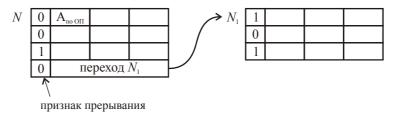

| Аппаратура прерываний                                   |     |

| Защищённая подсистема. Многоуровневая защита            |     |

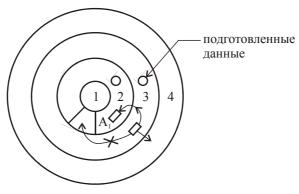

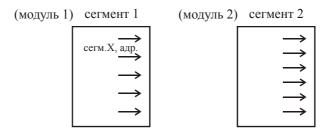

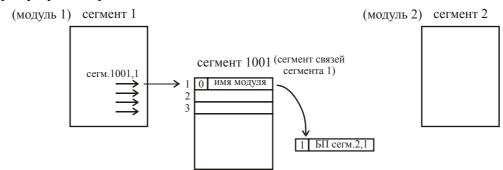

| Аппаратная поддержка взаимодействия программных модулей | 79  |

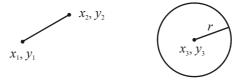

| Типы устройств внешней памяти и ввода-вывода            | 80  |

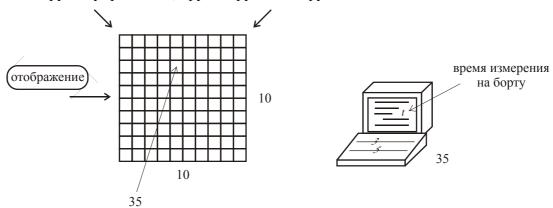

| Дисплеи                                                 |     |

| Диски                                                   |     |

| Печать                                                  |     |

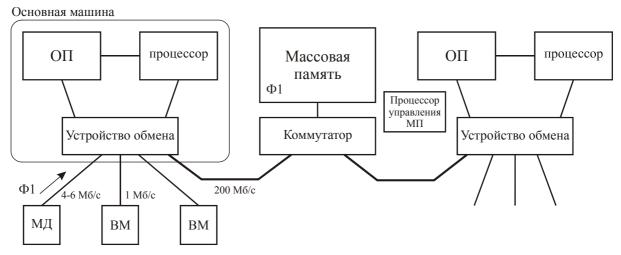

| Многомашинные комплексы                                 |     |

| Заключение                                              | 99  |

| Вопросы по курсу «Вычислительные системы»               | 101 |

| Литература к курсу «Вычислительные системы»             | 102 |

#### Введение

Сегодня мы начнём (будет много вводных предложений) курс: «Вычислительные системы» для 3-го потока 4-го курса. Фамилия моя Томúлин, Александр Николаевич, профессор кафедры АСВК со времён её основания, а также основания факультета, т.е. с 1970 года, когда её возглавил Лев Николаевич Королёв, которому послезавтра исполняется 80 лет. Будет большая конференция, будут выступать все его ученики, которых очень много, много всяких корреспондентов академии наук, докторов наук.

Лев Николаевич, конечно, это большая школа, школа программирования, школа разработки с точки зрения моделирования, проектирования архитектуры вычислительных машин и их использования. Очень развита школа и современных компьютеров. Ну так вот, он человек совершенно замечательный, человек очень дружественно расположенный, ну, собственно говоря, он мой научный руководитель был, да и сейчас коим, конечно, является. И, конечно, все кто его знает, те отмечают его исключительное дружелюбие, исключительный такт в общении, исключительно положительную настроенность. Вот я сообщаю вам положительный факт, что в хорошем настроении, в хорошей отдаче живёт наш замечательный профессор Лев Николаевич Королёв, выпускник механико-математического факультета МГУ, воевавший на фронте в Великую Отечественную войну. Тут больше ничего не добавить.

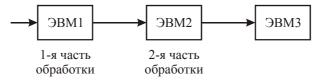

Вычислительные машины вначале так и назывались — «вычислительные машины». Слово «компьютер», во всяком случае, в нашем отечественном лексиконе, привилось далеко не сразу. Но уже, когда вычислительные машины стали обладать многими уровнями параллелизма, подсоединениями многих внешних устройств, каналов, высокий потенциал внутренних устройств развивался всё больше с развитием параллельной обработки информации в самих центральных устройствах машины, их стали называть вычислительными системами. Ну и конечно объединение вычислительных машин, оно началось с самого начала. Как только в какой-то организации появилась вторая машина, так сразу появился уже двухмашинный комплекс. И это, естественно, для разных целей. Вторая машина, как правило, являлась более производительной, на неё и перекладывалась задача обработки информации, а предыдущая машина приспосабливалась к выполнению функций ввода-вывода. Или, если машины одного уровня производительности, то они использовались и для разделения труда по обработке информации, для резервирования в случае таких систем, как когда в случае выхода из строя одной машины тут же переключаться на продолжение вычислений с сохранением информации на каком-то этапе на внешней памяти машины. По разным причинам возникали эти многомашинные комплексы. Т.е. они возникли на много раньше многопроцессорных. Ну и продолжают существовать и сейчас.

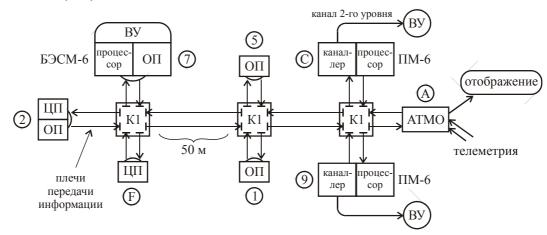

Кстати, о том, что они были актуальны: как-то, после того, как уже было выпущено какое-то количество машин БЭСМ-6, была конференция на Украине в палаточном городке Института кибернетики Академии наук Украины. Конференция была такая: «Связь БЭСМ-6 с другими ЭВМ». И выяснилось, что число многомашинных комплексов (от 2-х и более машин в каждом комплексе), в который входит машина, БЭСМ-6 в Советском Союзе превышает количество выпущенных машин БЭСМ-6. Это вот что касается вообще понимания вычислительных систем. Ну а затем стали появляться многопроцессорные вычислительные комплексы. Сейчас существуют системы с громаднейшим количеством процессоров. В данном случае сейчас это всё на микропроцессорах строится, на достижениях технологий последних десятилетий. И эти системы — они требуются. Постоянно возрастают мощности машин в списке TOP500 (http://www.top500.org) — это список наиболее высокопроизводительных вычислительных машин в мире. И вот, в каждом новом списке они несколько раз в год меняются. Сейчас эти наиболее высокопроизводительные установки — это десятки и уже даже сотни Тфлопс, т.е. тысяч миллиардов операций в секунду. Но это именно Тфлопс, т.е. операции над числами, представленными в системе с плавающей запятой, полноразрядными. Конечно, это для вычислительных задач существенно. Правда, есть задачи, которые не требую большого количества арифметических операций над числами с плавающей запятой, логические задачи. Но так уж традиционно, вычислительные машины с самого начала производились для вычислительных задач, но поскольку их область применения расширилась у вычислительных систем так же, но, как видите, оценивается в Тфлопс. Ну, т.е. есть Мфлопс, есть Гфлопс (миллион операций в секунду с плавающей запятой). Кроме того, есть MIPS (million instruction per second) — это количество операций, проходящих через устройство управления машины. Вовсе не все эти операции участвуют в арифметических вычислениях. Есть какието операции подготовки, считывания данных, какое-то ещё преобразование для дальнейшего использования в вычислениях. Поэтому, как правило, даже для счётных задач вот таких операций с плавающей запятой (это, собственно говоря, операции  $+, -, \times, \div$ ) их от числа всех операций приблизительно 1/3. Да и вообще надо смотреть в контексте, когда говорят о числе операций в секунду, что это за операции. Если это операции действительно над числами с плавающей запятой да ещё 64-х разрядными числами.

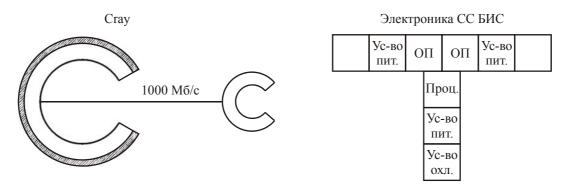

Вот такой гротескный пример. Как-то довольно давно в зале президиума академии наук обсуждался ход разработки отечественных суперЭВМ, которые по своей архитектуре, структуре да и возможностям не на много уступали состоянию дел американской техники того же времени. Конструктор рассказывает, какие проблемы есть с организацией электропитания, организации охлаждения. И этот вопрос мы с вами тоже рассмотрим, что очень интересно, какие пертурбации произошли за какой-то период. В технической реализации вычислительных систем был момент, когда казалось, что всё: наступает тепловая смерть вычислительной техники. Как когда-то, не то, чтобы я увлекался шахматами, но интересно было исследовать этот вопрос. И вот в своё время, как в мире, так и в литературе, говорилось, что всё: мир ждёт ничейная смерть шахмат. Потому что сейчас самые выдающиеся гроссмейстеры друг другу ни в чём не уступают, и не будут уступать. И всё большее число людей будут становиться столь совершенными в этом вопросе, что выиграть на одном уровне будет просто не возможно. Турнир будет обречён на погибание: это же не интересно, когда практически все встречи будут заканчиваться вничью. К счастью этого не случилось до сих пор, но угроза такая существовала. Так же и тепловая смерть вычислительной техники, т.е. ситуация сводилась к тому, что уже на столько быстро протекают процессы в интегральных схемах, что при большой частоте разогревается схема. Это естественный физический процесс. Нужно отводить тепло. Начали схемы помещать (машина Cray, которую мы будем рассматривать как образец достижения нескольких уровней параллелизма информации от первой до следующей) на трубу, через которую протекает хладагент, отбирая выделяемое тепло. Потому что каждая схема выделяла 5 Вт, этих схем было очень много, и если это охлаждение убрать, то человек в момент вспыхнет, и в этом пламени ничего не останется от этой машины. Конечно, приходилось очень следить за тем, чтобы система охлаждения правильно работала. Если неправильно, то нужно отключать. Специально систему мониторинга для этого вывели, и машина этим контролировалась.

Стау достиг производительности 1 Гфлопс (миллиарда операций в секунду). Но это дело уже 80-х гг. Потом для достижения большей производительности от фирмы Стау некая американская фирма «Эта» решила достичь 10 миллиардов и вынуждена была окунать всё оборудование процессора и памяти в криогенную среду, т.е. с высокой степенью охлаждения, чтобы отбирать это тепло. Тогда были частоты порядка 100 МГц.

За счёт интенсивных исследований был достигнут исключительный прогресс. В результате при тех же скоростях перешли обратно от водяного охлаждения или даже вот такого вот экстремального, перешли обратно к воздушному охлаждению. На это тратились огромные усилия разработчиков, ну и развивались технологии не только самого вычислительного дела, но и многие технологии материаловедения в мире. Вычислительная техника была заводчиком этого дела.

И вот в этом TOP500 вы можете всё увидеть. У нас, кстати, есть TOP50 (<a href="http://www.supercomputers.ru">http://www.supercomputers.ru</a>) — это список наиболее производительных вычислительных систем, установленных в России и странах СНГ (по-старому — в Советском Союзе). Имеются тоже крупные системы, наиболее крупная система — 15 Тфлопс, установлена в так называемом здании президиума академии наук с высокой навороченной верхушкой, Ленинский проспект, дом 32. Почему «так называемом», потому что сам президиум академии наук там не сидит. Он сидит по прежнему в прекрасном особняке среди зелени, отодвинутом от шум-

ного Ленинского проспекта, на Ленинском, 14. Так вот, там находится известный суперкомпьютерный центр, очень хорошо оснащенный входными телекоммуникациями, естественно внутренней сетевой средой. Там не одна, несколько машин. Но вот одна из наиболее производительных — это машина 15 Тфлопс, разработанная у нас, однако на зарубежных микропроцессорах, хороших, конечно, и т.д., но вот, тем не менее, такова сейчас ситуация.

Кстати, на это вы можете выйти через сайт НИВЦ МГУ: <a href="www.parallel.ru">www.parallel.ru</a> — это сайт вычислительного центра, созданный коллективом и под руководством Владимира Валентиновича Воеводина (сейчас там зам.директор ВЦ), выпускника кафедры АСВК. Сайт замечательный: там есть и история, и все характеристики современных различных классов высокопроизводительных вычислительных систем, там есть и рассмотрение фирм, учебные материалы там представлены наших сотрудников, ВМиК и Петербургского университета.

Какова же будет наша с вами задача? Конечно, как специалисты в области программирования, вы должны быть грамотны в области состояния современных вычислительных систем разных классов, разного назначения использования, применения. Поэтому эта цель естественна. Она достигается в обзорном порядке в каком-то смысле, потому что рассмотреть подробно все вычислительные системы не представляется возможным. Но эта цель попутная, которую мы должны достигнуть. Какая же цель главная? А главная цель такая: рассмотреть развитие идей в области архитектур, структур вычислительных систем, развитие мышления конструкторов, разработчиков средств поддержки развития архитектуры, интегрирования. А рассмотрение развития их мышления — это есть основа развития собственного мышления, и вашего, и моего, и всех тех, кто работает в нашей области. Поэтому вот это мы будем рассматривать в первую очередь. На базе какого основного стержня мы будем это рассматривать? На базе стержня рассмотрения развития параллелизма обработки информации в вычислительных системах. Естественно здесь будут привлекаться исторические аспекты. И рассматривая всё более новые и новые уровни развития параллелизма, достигнутые разработчиками вычислительной техники, на примере машин, наиболее хорошо отражающих появление и реализацию этих идей, мы и будем вести рассмотрение нашего курса. В какой-то мере будет повторение, может быть в несколько новом аспекте, некоторых моментов, которые у вас были и в курсе ЭВМ, и программирования, может быть ещё где встречались. В этом нет ничего плохого, это только хорошо и послужит вам для закрепления этого всего материала.

Конечно, есть компромисс между тем, что решается аппаратно (на уровне hardware), и тем, что решается программно (на уровне software). Этот компромисс существовал всегда. В какой-то момент, hardware, развившись до какого-то уровня, позволило существенно развить software. Кстати, есть очень интересный момент в этом смысле при создании машины БЭСМ-6. Когда была создана машина БЭСМ-6, вдруг было создано 5 операционных систем, 6 автокодов (языков и, соответственно, трансляторов ассемблера с этих языков). Потом, в конечном счёте, конечно, всё это свелось к одной-двум системам, активно используемым и хорошо поддерживаемым. Зачем всё это было произведено? Казалось, что в каждом конкретном случае есть определённые причины. Например, в Институте прикладной математики (ИПМ), который возглавлял президент академии наук Мстислав Всеволодович Келдыш, он очень ревниво относился к приоритету своей организации в самых разных вопросах: в вопросах вычислительной математики и в вопросах программного обеспечения. Поэтому появилась ОС ИП. Казалось бы в этом причина. Появились операционные системы варианты на Урале, появилась операционная система, естественно, в организации, создавшей машину — Институт точной механики и вычислительной техники, Ленинский, 51. Тут и Лев Николаевич Королёв, Виктор Петрович Иващенко, заведующий кафедрой системного программирования, и ваш покорный слуга являются альма-матер, для которого кроме, естественно, факультета это этот институт во главе с академиком Сергеем Алексеевичем Лебедевым основателем отечественной вычислительной техники. Оттуда, собственно, сюда пришёл Лев Николаевич Королёв, ну и продолжает работу ту же самую: создание новых машин и программного обеспечения. Институт покинул, но работает параллельно в том же направлении.

Вот казалось бы, что везде есть своя причина появления нескольких ОС и автокодов. На самом деле, это были поводы. А причина была очень глубокой: появилась среда (машинная) и возможность развить себя, создать сложную программную систему, т.е. таким образом развить своё мышление на имеющихся средствах, т.е. в машине (создать для неё). И готовые к этому коллективы, где эта потребность существовала, она прорвалась, и люди сделали эти вещи, развив тем самым себя и создав основу для затем продолжения разработки других. Т.е. речь идёт вот о чём: в своё время постулаты диалектического материализма (это вещь наблюдательная, это выводы, сделанные на основе наблюдения окружающего нас мира). Вот одним из положений диалектического материализма было такое (потом это положение убрали и понятно почему): мир развивается по законам развития живой и неживой природы, нам неподвластным. Отсюда следует, что это либо от божественного начала, либо от «большого взрыва» — образовались какие-то физические константы и всё дальше идёт. Человек может лишь временно ускорить где-то или замедлить этот процесс, но повлиять кардинально на его изменение не может. И действительно, повинуясь этому закону, вот эти появились параллельные разработки. Потом этот постулат убрали, потому что никак не совпадало с руководящей и направляющей ролью коммунистической партии. Точно так же, повинуясь этому закону развития производительных сил, сразу несколько групп исследователей пришли к разработке вычислительных машин.

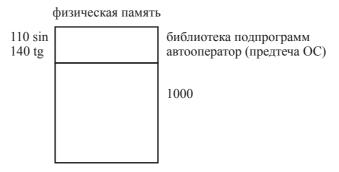

Первой вычислительной машиной считается машина ENIAC, разработанная американскими учёными Джоном Мачли и Джоном Проспером Экертом (на электронных лампах). Эта машина была не машиной с хранимой в памяти программой. Это была электронная вычислительная машина, но программа набиралась на штекерных устройствах. Поэтому полностью электронной вычислительной с хранимой программой назвать нельзя. Тем не менее, считается первой электронной вычислительной машиной. Но параллельно с американцами шла разработка и у нас С.А.Лебедевым в Киеве тогда (потом уже и здесь). Сам он родился в Нижнем Новгороде в 1902 году, и он также развил эти идеи. Он был одним из беднейших мировых учёных электротехники: расчёт линий электропередач, регулировки электрогенераторов, у него было много книг. И вот будучи 40 с чем-то лет отроду, он занялся созданием вычислительных машин. Дело в том, что тогда на специальных анализаторах, моделирующих решение дифференциальных уравнений на процессах протекания электрического тока, проводились расчёты, и это их устраивало: и точность и время. И, видимо, это толкнуло на то, чтобы создавать средства расчетов, которые ему были необходимы в своей активной деятельности. Потом он полностью переключился на деятельность в области вычислительных машин. И уже в 50-м году появилась Малая электронная счетная машина (МЭСМ) в Киеве, она была самой производительной машиной в Европе, которая была уже машиной с хранимой в памяти программой.

Параллельно с Лебедевым этими же вопросами занимался и другой отечественный исследователь и его группы — это Исаак Семёнович Брук. И если Лебедевым была основана школа высокопроизводительных машин, то Брук — школа малых машин, управляющих машин, которые предназначались для управления различными производственными объектами, для малых вычислений.

Так вот смотрите: оба родились в 1902 году с разницей в несколько дней (Лебедев — 2-го ноября, а Брук — 8-го ноября), оба сдали первые вычислительные машины (Лебедев в Киеве, Брук в Москве) в одном и том же 51-м году почти одного и того же числа (25 декабря) Государственной комиссии. Оба умерли в 1974 году с разницей в 2 месяца. Случайны ли эти совпадения?

А потребности, конечно, были. Для этого делались попытки механизации вычислений — это машина Бэббиджа (ещё у него первой программисткой была его дочь). Многие другие исследователи делали это дело.

За рубежом есть премии Computer Pioneers (общество III) — они даются живым людям — пионерам вычислительной техники. И вот несколько лет тому назад этой премией наградили 3-х, но уже не живых, пионеров вычислительной техники нашего отечества, а именно С.А.Лебедева, А.А.Ляпунова и В.М.Лужкова. Аргументация была такая: в связи с железным

занавесом, не возможно было получить достоверную информацию по достижениям учёных, и после того, как это удалось сделать, стало ясно, что они являются полноправными участниками мировой шеренги, общество решило эти медали вручить.

После МЭСМ почти сразу появилась машина БЭСМ — большая электронная счётная машина академии наук — разработка коллектива С.А.Лебедева.

И вот первая международная конференция в Кронштадте в 1955 году, где подводились итоги первого десятилетия компьютерной эры. На эту конференцию едет наша делегация. Из-за всяких проволочек наши приехали, когда конференция закончилась: конференция закрылась и в зале появляются наши. Но т.к. доклад Лебедева был запланирован, решили собраться на утро следующего дня: собралась вся конференция, Лебедев сделал доклад, было признано, что это самая высокопроизводительная машина в Европе, практически равная американским вычислительным машинам того времени. И сразу было выпущено несколько описаний этой машины на английском, французском и немецком языках.

Таким образом, наши разработки ни сколько не уступали американским аналогам, и даже кое-где их превосходили. Долго мы не проигрывали в области архитектуры, структуры, программирования, и начали проигрывать технологии с какого-то момента времени.

Появилось довольно много различных конструкций, появились высокопроизводительные машины. В 60-х годах появилась машина БЭСМ-6, которая практически совпадала по параметрам с зарубежными аналогами. Появились разные другие машины: в Минске — «Минск», появились малые управляющие машины (последователи Брука), вычислительные комплексы для систем реального времени. Потом появился Научно-исследовательский центр электронной вычислительной техники (НИЦЭВТ). Направление машин единой серии (ЕС) — это головное направление разработок НИЦЭВТ.

В 1956 году прошла конференция, где Лебедев высказал идеи, все те, которые сейчас реализуются: идеи сверхбыстрой оперативной памяти (кэш), идеи многопроцессорности. Интереснейший был доклад, и конференция называлась совершенно музыкально: «Пути развития советского математического машиностроения».

Естественно, что программисты писали очень хорошие программы, старались максимум ужать, ускорить, уменьшить количество используемых ячеек памяти. Сейчас как говорят: «У тебя медленно работает? Купи ещё сколько-то мегабайт памяти!» Но даже на имеющихся мегабайтах памяти можно в 10 раз уменьшить, в 100 раз ускорить, но годочек посидеть над этим делом. Это всё идёт от зарубежных фирм: приходит человек на работу, вот тебе задание. Он говорит: «Я могу сделать это очень хорошо, но мне нужен год» — «Нет, ты сделаешь это за 2 недели, используя имеющиеся средства» — «Да, но это будет неэффективно!» — «Чёрт с ним! Им не понравится, будет медленно, пусть купят новую машину. Она с большей частотой и тогда у них будет проходить нормально». Есть даже сведения, что в некоторые места в операционных системах вставляются задержки, чтобы вам было менее комфортно, и вы купили новую машину! Главное — быстро вывести на рынок.

Момент по системе противоракетной обороны. Это был многомашинный комплекс. Под руководством Всеволода Терентьевича Бурцева, а программный комплекс делался под руководством Льва Николаевича Королёва, этот комплекс на машине М-40 (40 тысяч операций в секунду, память — 4 килослова). И на этом работали программы системы жёсткого реального времени. Первое испытание — 1961 год (американцы подобное сделали только через четверть века), и в первое же испытание первой же ракетой была сбита нападающая баллистическая ракета — восторг! А всё записывалось: получаемые данные, выдаваемые данные и т.д. Дело в том, что подрыв заряда противоракеты должен происходить, когда расстояние до нападающей ракеты было порядка 25-30 метров. Если больше, то смысла нет. И вот когда всё проверил, то оказалось, что расстояние было значительно больше. В чём же дело? Оказалось, что всё произошло по ошибке программиста: расстояние определилось как маленькое, произошёл подрыв, и т.к. конус разлёта осколков был удачным, то нападающая ракета была сбита. Потом научились сбивать, как отче наш.

Потом научились проигрывать имеющуюся музыку, писать новую. Выпускник мехмата 58-го года, прима артист театра МГУ Андрей Михайлович Степанов как раз писал програм-

му определения траектории нападавшей ракеты. А потом написал программу воспроизведения музыки на машине БЭСМ-6: 6 динамиков вешались на 6 разных регистров, он задавал программу, которая как-то закодированные ноты переводила в коды, которые передаются на регистры. Ни один орган в мире не мог воспроизвести подобного. А потом он написал программу сочинения музыки строгого стиля а-ля фуги Баха. Музыку записывали на магнитофон и проводили заслушивание на учёном совете в консерватории. После прослушивания встал из них самый главный и сказал: «Своим студентам за эти произведения я ниже «тройки» бы не поставил». А потом шла программа разворота противоракет — программа жесткого реального времени: рассчитывались поправки на машине и передавались указания на рули — за 0,1 с — это была программа Геннадия Георгиевича Рябова.

Вспомнился анекдот про диалектику из серии анекдотов про Петьку и Василия Ивановича:

Петька спрашивает у Василия Ивановича:

- Скажи, пожалуйста, ты в верхних кругах вращаешься, что такое «диалектика»? На что Василий Иванович отвечает:

- Это, Петя, такая тонкая материя. Так вот на словах не объяснишь. Давай я тебе пример?

- Ну хорошо, Василий Иванович, давайте.

- Ну вот: встречаются два солдата один чистый, другой грязный. Перед ними баня. Который пойдёт в баню?

- Грязный пойдёт.

- Нет, Петенька. Чистый пойдёт. Он привык себя блюсти. А грязный... Ну ты же знаешь нашего брата солдата.

- Совершенно верно! Именно всё так и бывает. Вы совершенно правы, Василий Иванович. Всё так и будет.

- Хорошо. В другой день встречаются два солдата один чистый, другой грязный. Который пойдёт в баню?

- Чистый же пойдёт. Вы же сами говорили...

- Нет, Петенька. Грязный пойдёт в баню. Его вошь на столько заела, что сил уже нет. А чистый подождёт.

- Истинно так! Всё так и будет. Как Вы говорите всё правда.

- В третий раз встречаются два солдата один чистый, другой грязный, перед ними баня. Который пойдёт в баню?

Далее следует специфический энергичный взгляд со стороны Петьки, на что Василий Иванович и отвечает:

— Вот, Петя. Это и есть диалектика.

Как же быть с Джоном фон Нейманом? Все говорят: «архитектура фон Неймана», «машина фон Неймана» и т.д. Всё что нас окружает, все установки (большие и малые, персональные), всё это — машины архитектуры фон Неймана. В чём тут дело? А дело вот в чём. Фон Нейман — это знаменитый очень известный математик, по происхождению — американец, был очень известным учёным в 40-х годах. Есть масса книг о нём. Джон фон Нейман участвовал в атомном проекте, видел то, что для крупных проектов не хватает имеющихся средств. Он, конечно, заинтересовался первой машиной, которая была сделана до него, но он не принимал участия в создании вот этой первой машины ENIAC. Он заинтересовался, включился в коллектив разработчиков, и уже следующая машина была создана с его участием. Как крупный учёный, он обобщил имевшиеся до него достижения, и опубликовал основные принципы (так они и стали называться «принципами фон Неймана»), а архитектура, соответствующая этим принципам стала называться архитектурой фон Неймана. Что это за принципы: это управление программой, которая храниться в памяти машины, это двоичная система счисления, набор операций (арифметических, логических), управление, переход на

другие ветви вычислений и т.д. Так что, с одной стороны он не является родоначальником этого дела, с другой — он активный участник этого процесса.

В противовес появляются машины, управляемые потоком данных (не командами). Если у вас достаточно в машине оборудования, то эта машина действительно потоком данных реализует заложенный в алгоритме параллелизм. Конечно, команды как-то заложены, но опосредовано. Важно, что получающийся результат какой-то операции находит себе пару в ассоциативной памяти, и вместе с этой парой (обычно двуместные операции) там идёт кодирование операции. Т.е. она не выступает как главное действующее лицо, а как подчинённое. Такая ассоциативная память становится устройством управления. Управление осуществляется путём сравнения. Конечно, программирование здесь очень сложное, и хотя заманчиво иметь полный параллелизм, но до сих пор таких машин в мире в больших количествах нет.

Лебедев со своими лучшими учениками выполнял проект интересной машины Dataflow (управляемой потоком данных). И сейчас этот проект продолжается, но под руководством А.М.Степанова.

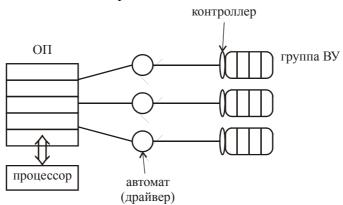

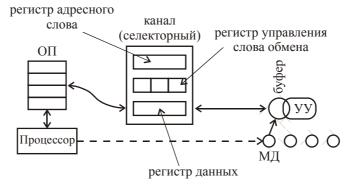

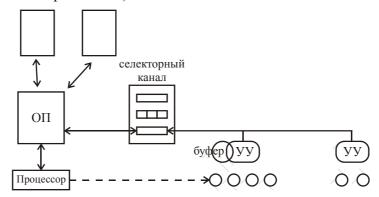

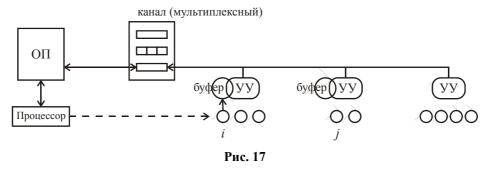

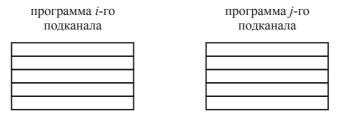

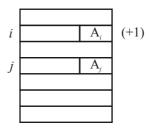

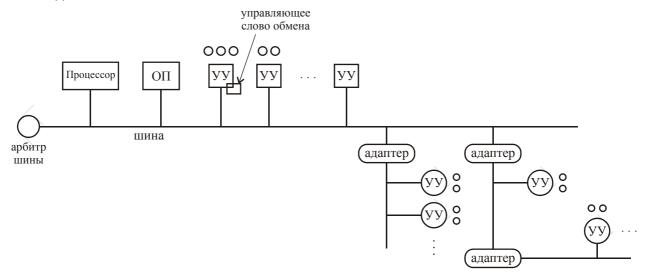

Есть понятия «архитектура ЭВМ» и «структура ЭВМ». Особенно нехорошо сейчас обстоит дело с термином «виртуальность». Что такое «структура ЭВМ»? Скажем так: вот у вас есть какие-то каналы связи с внешними устройствами одного типа или другого типа (селекторный или мультиплексный, какой-то канал на базе общей шины, к которому подсоединяются многие устройства). Работу этих кагалов обслуживает операционная система, и для пользователя это может быть совершенно не интересно, ему это не важно. Какому угодно пользователю: прикладному, системному. Вот это — структура ЭВМ. Сколько у вас памяти сверхбыстродействующей, в которой автоматически накапливаются наиболее часто используемые данные (память cache). Одноуровневый, двухуровневый. Это к программированию никак не имеет отношения. Вот это структура — внутренняя организация, которая никак не отражается на проблемы программирования. А вот архитектура ЭВМ... Есть два основных подхода. Первый — чёткий — система команд машины. Например: вот у вас система команд для выполнения действий над числами, представленными с фиксированной запятой; другая система команд — для чисел с плавающей запятой. Наборы команд совершенно разные. Ещё пример: содержаться команды обработки векторов или не содержаться. Если таких команд нет, то выполняется обработка циклом. Вот это существенно. Второй подход — более расплывчатый в том смысле, что описывается система в виде некоторой многоуровневой системы. Естественно уровни аппаратуры, уровни системного ограничения, уровни библиотек, уровни middleware, прикладные программы, административный уровень и т.д. И обязательно интерфейсы между уровнями.

Мы с вами обсуждали, что был период «золотого века» отечественной вычислительной техники, когда наши разработчики, инженеры, программисты находились над уровнем зарубежных коллег. Это признавалось и сейчас во всех исследованиях признаётся. Сейчас же нас существенно обошли. Этому есть ряд причин. Что же на самом деле произошло?

Статья «Москва компьютерная» (<u>www.computer-museum.ru</u> — сайт виртуального компьютерного музея — раздел «Развитие вычислительной техники в СССР») была заказана к 850-тилетию Москвы:

«...Компьютеростроение стимулировало и вбирало в себя лучшие достижения смежных областей науки и техники: сначала — электроники, а затем и микроэлектроники, вложившей информационную мощь в миллионы мельчайших транзисторов. Микроэлектроника в последние 15–20 лет стала главной движущей силой компьютерной революции. В результате в условиях открытого информационного пространства в мире сформировалась массовая компьютерная индустрия, осуществляющая принципиально новую социальную функцию: обеспечение лавинообразного накопления информации, которая становится главной регулирующей силой жизни человечества.

...В конце 40-х годов к созданию ЭВМ оказались готовы только три страны: США, Англия, СССР. Для разработки, развития и применения средств вычислительной техники (ВТ) необходимы следующие условия:

- постановка масштабных актуальных задач, не поддающихся решению без применения средств ВТ;

- наличие технической инфраструктуры и передовых технологий для разработки и применения ВТ;

• наличие вузов с профессорско-преподавательским составом, способным вести подготовку кадров в данной области...

#### Быть или не быть?

Всякое новое социально-значимое явление в жизни человеческого общества подвергается со стороны власть предержащих самой тщательной проверке и экспертизе. Так велит закон самосохранения власти. Колоссальная роль вычислительной техники для будущего — не только как новой области науки и техники, но и как принципиально нового фактора социального влияния — стала предметом пристального внимания политиков и идеологов с обеих сторон "железного занавеса".

В начале 50-х годов в США по инициативе правительства (о чем у нас почти совсем неизвестно) была развернута общественная дискуссия на тему "Несут ли компьютеры угрозу американскому образу жизни?". Правящие круги испытывали серьёзные опасения из-за возможного нарушения баланса на рынке труда. К экспертизе социальных последствий были подключены активно работавшие в области кибернетики ученые с мировыми именами: Дж. фон Нейман, Н. Винер, К. Шеннон и др. Вердикт всесторонней и независимой экспертизы поражает своей дальновидностью: при грамотном использовании компьютер усилит позиции общества, основанного на свободной конкуренции. Только после этого власти США дали зеленый свет свободному рыночному развитию вычислительной техники.

Этот шаг, на первый взгляд, локального (для одной страны) значения воспринимается сегодня как открытие, масштабы которого только начинают осознаваться социологами. Широкое и свободное развитие вычислительной техники с неизбежностью приводит к созидательной информационной трансформации общественного сознания в целом.

Так искали и находили ответы на вопрос "быть или не быть" власти на Западе. В нашей стране блюстители идейной чистоты, к сожалению, поспешили определить кибернетику, а вместе с ней и вычислительную технику, как "буржуазную лженауку". Чтобы лечить "болезни" с таким диагнозом, надо было иметь гражданское мужество. В защиту вычислительной техники активно выступили академики А. И. Берг, А. А. Дородницын, С. А. Лебедев. В результате в эшелонах власти вычислительная техника получила зеленую улицу, но только для решения задач достижения военного паритета. Ревнители идей обобществления вслепую отвергли для широкого общества то огромное богатство обобществленной собственности, которое сейчас лавинообразно реализуется в среде мировых информационных ресурсов. Таковы парадоксы истории...»

Раньше был лозунг: «От каждого по способности, каждому по труду, его общественнополезных результатов». Первое как-то достигалось: никто не мешал работать, кто не хотел — тот не работал (недостаток был). А вот «каждому по труду» — это не получалось. Таким образом, выдвинутый лозунг для существования общества оказался нереализованным. Отсюда и крах общества: уравниловка и прочие.

Когда мы работали, мы видели — вокруг дело новое, а вот это — дело тёмное. Поэтому, конечно, хотелось что-то сделать, да ещё к тому же, понимая, что это нужно для развития общества. Нас поддерживало то, что оценивалась наша работа не хуже других направлений деятельности в нашей стране. И это создавало хорошее настроение.

Сейчас этот лозунг тоже не достигается (от каждого по способности, каждому по труду). К сожалению, произошло резкое расслоение. И те, кто получает что-то большое, это уже не по труду, не по количеству вложенного в общество. А просто-напросто у него оттягивает. Т.е. переход на новые рельсы жизни лоббируют в первую очередь те, кто потащили на себя одеяло государственных средств.

Что делается в Америке? А в Америке делается следующее: как только подназревает новый этап, чтобы поддержать конкурентную способность Америки, они выделяет сотни миллиардов долларов на развитие программного обеспечения супермашин. Куда? Конечно, безвозвратно!

«...История не злонамеренна. Она дает шанс всем, кто в нем нуждается. Сегодня мы должны и можем начать вторую попытку. Но для этого надо до конца выправить идейные ошибки прошлого, которые обрекли страну на самоизоляцию.

Вплоть до переломного момента начала реформ Москва оставалась для страны компьютерным локомотивом. Налицо парадокс: лидеры реформ, сумевшие снять с великой страны "железный занавес", не видят для нее своих путей к информационно-компьютерному суверенитету...»

Им не дают видеть негодяи, которые всю страну направили на собственное накопление.

«...Накопленный в стране интеллектуальный потенциал, способный активно влиять на будущее страны, остается невостребованным. Неужели на ухабах реформ Москва отказалась от бремени лидерства? Не хочется думать, что после 850 лет преодолений на очередном затяжном подъёме стало невмоготу крутить компьютерные педали».

Статья давняя, но всё-таки достаточно актуальная.

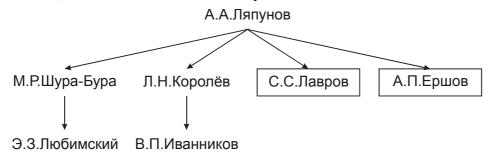

А.А.Ляпунов считается основателем программирования. М.Р.Шура-Бура — долго возглавлял кафедру Системного программирования, затем был В.П.Иванников. М.Р.Шура-Бура возглавлял всё это дело в Институте прикладной математики (ИПМ), Л.Н.Королёв — в Институте точной механики и вычислительной техники. И всюду работали до кафедры и в содружестве, и в соперничестве по вопросам системного программного обеспечения. С.С.Лавров — он работал и по программированию космических дел, потом возглавлял программистов по тем же делам в Вычислительном Центре Академии наук. Э.З.Любимский сейчас возглавляет центральную комиссию в Институте прикладной математики (ИПМ). А.П.Ершов — член-корреспондент Академии наук, выдающийся человек, есть школы и институты его имени по информатике.

Ладно, теперь к делу.

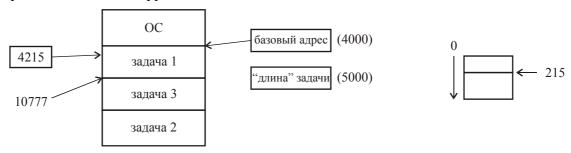

Есть 5 групп вопросов. Первая группа — это вопросы по параллелизму как внутри вычислительной машины, так и по параллелизму многопроцессорному. Вторая группа — это средства поддержки работы операционных систем. Третья — это организация памяти. Четвертая — это тоже для параллелизма важно — это различные способы подключения, различные каналы связи с внешними устройствами. И пятая — это многомашинные комплексы.

#### Классификация архитектур вычислительных систем

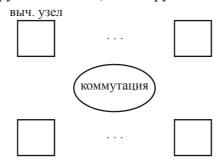

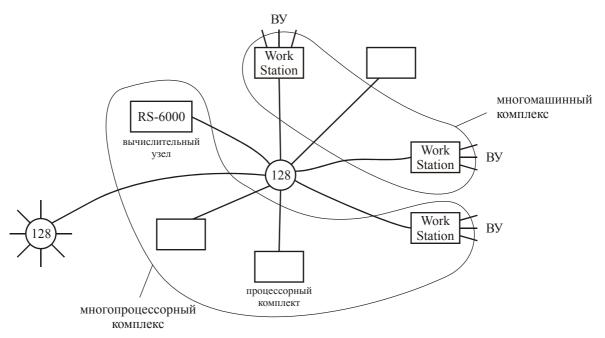

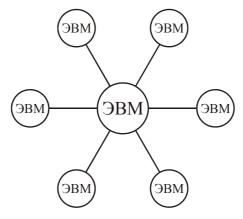

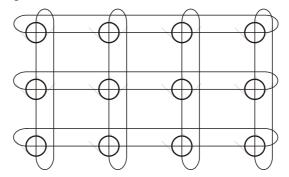

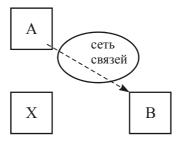

Мы с вами говорили о том, что вначале были многомашинные комплексы, пока ещё не было многопроцессорных. Потом появились многопроцессорные, параллельно существовали многомашинные комплексы. Существуют многомашинные многопроцессорные — каждая из машин многопроцессорная, машины соединены между собой. Логическое подмножество многомашинных комплексов — это сети ЭВМ. Мы с вами изучать сети не будем.

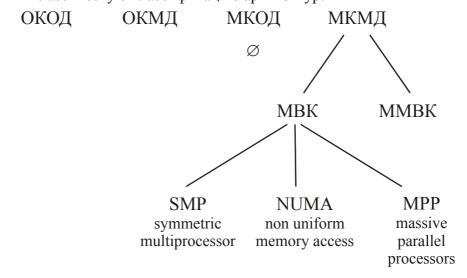

Напомним классическую классификацию архитектур:

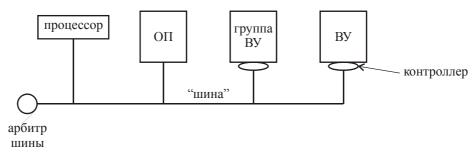

ОКОД — одиночный поток команд одиночный поток данных — один процессор. Что важно — одно устройство управления (УУ). Общее арифметико-логическое устройство (АЛУ). По-английски это — SISD (single instruction single data).

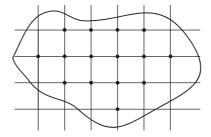

ОКМД (SIMD) — одна команда выполняется на разных процессорах над разными данными. Но одно УУ. Классический пример — ILIAC IV.

МКОД (MISD) — много команд, один поток данных. Попробуйте написать программу, которая бы имела операции +, -,  $\times$ ,  $\div$ , &,  $\vee$ , c d s u e только над одними данными (например, находящимися в ячейках памяти 3 и 6). Полная чушь! Такого не бывает. Этот класс пустой. Однако некоторые относят сюда машины с общей памятью: материал общий, над ним работает одна задача. Но у неё разные ветви, каждая ветвь идёт через своё УУ, это разные программы.

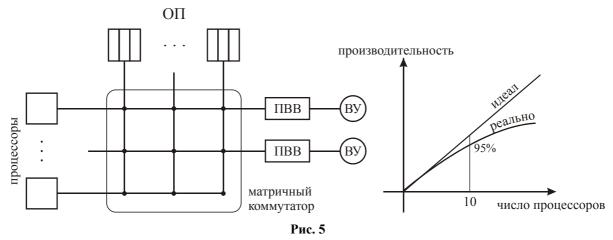

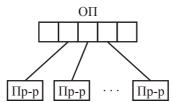

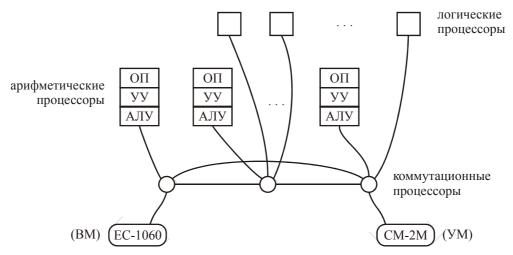

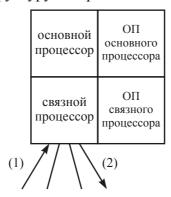

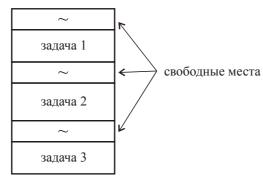

МКМД (МІМD) — подразделяют на 2 класса: многопроцессорные вычислительные комплексы (МВК) и многомашинные вычислительные комплексы (ММВК). МВК — это разные способы организации многопроцессорных комплексов, а именно SMP (symmetric multiprocessor), т.е. с общей памятью, в которой находятся данные, над которыми выполняются программы, выполняющиеся в разных процессорах. МРР (massive parallel processors) — это противоположный вариант — система, состоящая из многих узлов, в каждом из которых процессор и своя память, передача данных между ними идет сообщениями посредствам операционной системы. Т.е. именно из таких создаются комплексы на 1000 процессоров. И в промежутке NUMA (non uniform memory access) — вообще говоря, это идея общей памяти с точки зрения организации программирования. Узел так же как в МРР, процессор и память соединены общей шиной. Процессор может работать со своей памятью и с памятью другого узла. Ясно, что во втором случае процесс взаимодействия с памятью более долгий.

Только что прошла конференция, основным организатором которой был Московский университет в лице Вычислительного центра — «Интернет. Технологии параллельного программирования». Лидером во всех вопросах является Вычислительный центр МГУ. Надо сказать, что все ведущие фирмы учитывают эти моменты и как спонсоры они выступают здесь: IBM, Hewlett-Packard, Microsoft. Вещи очень актуальные, совершенно естественные.

Скажу вам прямо — я крайне недоволен докладами в области образования.

Дело в том, что в министерствах образования и науки, электронной связи и информатизации, в этих министерствах очень сильна чиновная прослойка, которая заботится только о себе. Это чистое растаскивание государственных средств. Им выгодно объявлять всяческие конкурсы, программы с очень расплывчатыми названиями, расплывчатыми позициями в содержании, потому что под это дело склонные до халявы люди с удовольствием подбираются. А чиновники потакают этому делу, и подбираются люди, которые занимаются якобы научной деятельностью и выдают якобы результаты этой деятельности. К сожалению, на конференции, не только на эту, это начинает проникать.

На прошлой моей конференции меня развели с этими людьми: дали мне заведовать другой секцией. На другой лекции были доклады, но нашлись другие, которые разумно покритиковали эти доклады. Но что толку критиковать? Это же просто пролезающая в нашу среду порча! И против этой порчи надо решительно выступать.

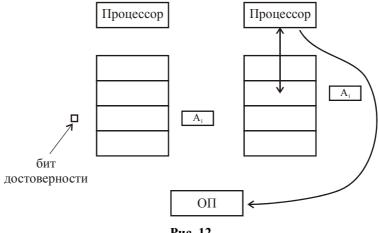

#### Параллелизм работы основных устройств машины

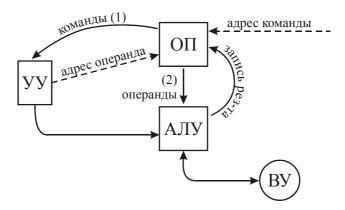

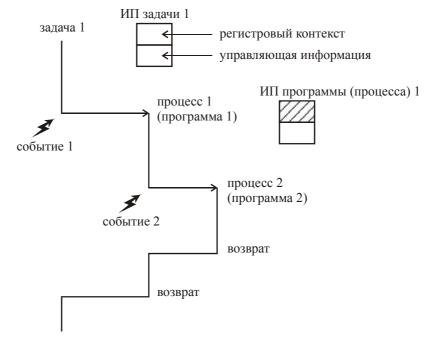

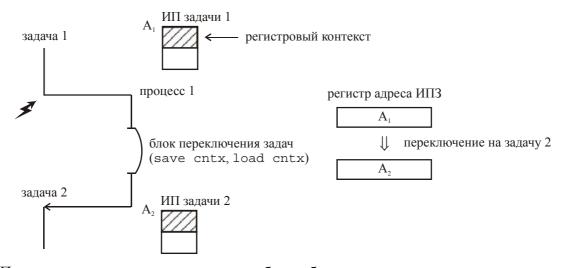

Мы с вами рассмотрим первый уровень параллелизма — это параллелизм работы основных устройств машины, который был достигнут в мире к концу 50-х годов. Вначале рассмотрим схему выполнения обработки информации, которая была в первых машинах.

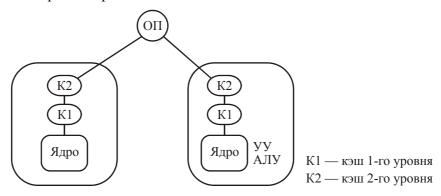

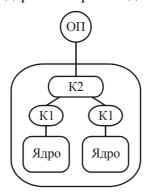

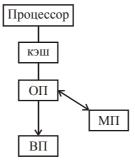

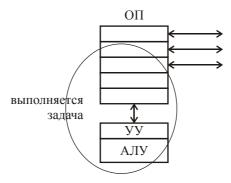

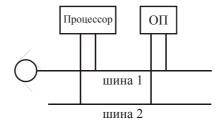

ОП — оперативная память, УУ — устройство управления, АЛУ — арифметико-логическое устройство. Попадая на УУ, операция вызывает из памяти тот операнд, который необходим. Первое действие — это выборка команды. Чтобы команду выбирать, подаётся адрес команды. Второе действие — подача результирующей информации. После того, как команда дешифрировалась на УУ, выполняется операция на АЛУ. В зависимости от системы команд, результат может либо сохраняться в регистре, либо записывается в ОП.

Итак, цикл: считывание команды — в это время задействована ОП, не работает УУ и АЛУ; когда считана команда, работает УУ, происходит дешифрация, передаёт адреса одного или нескольких операндов ОП, и эти операнды передаются АЛУ; потом работает АЛУ, а эти простаивают; ну и потом происходит запись результата (не обязательно в каждой команде).

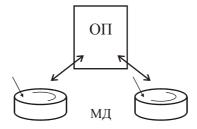

Очень интересно, как подключались раньше внешние устройства (ВУ) — магнитные ленты, магнитные барабаны, магнитные диски, печать и т.д. — подключались к АЛУ. Почему так? Потому, что вместо того, чтобы делать дополнительный тракт (усложнять машину), уже есть тракт передачи, и когда команда обмена данными между ОП и ВУ попадала в АЛУ, она там застревала до тех пор, пока весь массив данных не будет записан или помещён в ОП. Если вам нужно тысячу чисел передать в ОП, то операция здесь и стоит, пока это всё не окончится. Это всё потому, что машины были большие.

Ясно, что нужно обеспечить параллелизм работы этих устройств, сделать так, чтобы они не простаивали. Главное, конечно, это работа АЛУ, где выполняются операции. Вот если АЛУ работает 100% — это значит, что структурная схема машины идеальна. По целому ряду причин это не получается, и мы с вами эти вещи увидим.

Итак, нужно как-то организовать работу этих устройств, чтобы они работали параллельно. Ну и чтобы операции передачи данных на ВУ или приём данных с ВУ тоже выполнялись независимо от работы центральной части машины. Таким образом, память могла работать параллельно на выдачу команд, на выдачу операндов, на приём результатов и на работу с ВУ.

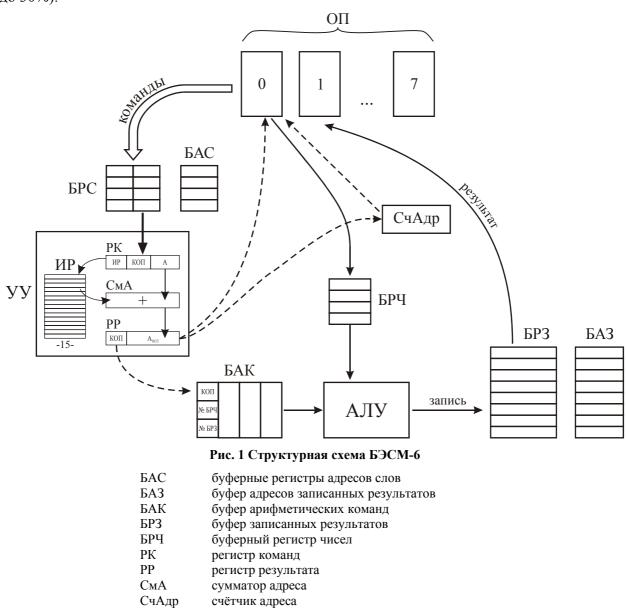

Машины были разные. Были машины одноадресные (решение вопроса организации параллелизма работы основных устройств на примере БЭСМ-6 (см. Рис. 1 на стр. 19) — эта машина была одноадресная). Были машины двухадресные, трёхадресные, четырёхадресные, ну и машины, так называемые, безадресные (когда у вас все данные находятся в определённом массиве — стеке — и вы работаете только со стеком, у вас программа идёт лишь что-то записать в стек, снять со стека — работа со стеком). Производительность работы машины в условиях вычислительного центра, где решаются самые разные задачи, осталась всё-таки независимой. В каком плане? Можно себе представить такое вычислительное ядро, которое требует только одноадресные операции. Для разных операций более эффективно использование какой-то определённой адресности. Поскольку и те, и другие сущности встречаются в вычислениях — это всё равно, какую систему использовать. Просто какая-то машина с какой-то адресностью будет более эффективна на отдельных участках вычислений, менее на других. Поставите другую машину — будет наоборот. Конечно, какая-то есть задача, в которой сущность вычислений требует наиболее эффективной одно- или двухадресной системы, но это уже будет неспециализированная машина. Зависимость от того, какого класса машина: для широкого класса задач, универсальная или специализированная машина.

В своё время, в системе противоракетной обороны была использована машина M-40 с системой команд работы с данными с фиксированной запятой. Безусловно, быстрее, чем с плавающей запятой, от природы. Но алгоритм развился, приходилось работать с данными разного масштаба, и необходимость масштабирования (загнать в определённый интервал от нуля до единицы) привела к тому, что вычисления всё дольше и дольше выполнялись. Тогда была сделана машина M-50 с плавающей запятой для тех же целей противоракетной обороны. Тогда появился интересный лозунг: «Какая лучшая специализированная машина? Конечно, универсальная!»

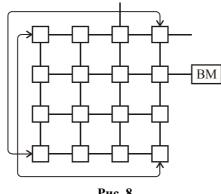

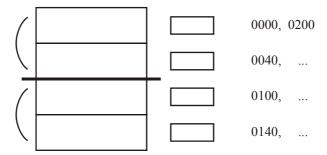

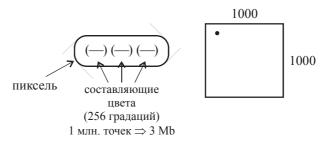

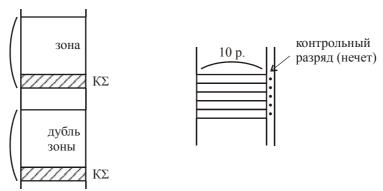

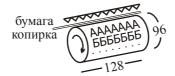

Итак, как сделать? Сразу напрашивается решение. Нужно сделать память так, чтоб можно было параллельно читать, параллельно записывать по нескольким запросам по разным направлениям. А как это можно сделать? Разбить память на несколько работающих блоков. Как сделать так, чтобы быстро шли одна команда за другой? В машине БЭСМ-6 адресация шла по словам (есть машины, где адресуются байты) — 48-разрядным словам. Мы подаём адрес на соответствующий блок, и после какого-то времени работы блока команда начала выбираться на УУ. Тут же мы можем, чтобы следующую команду подать как можно быстрее вслед за первой, мы прибавляем единичку к счётчику адреса слова, ответ должен пойти в память. Куда? В этот же блок? Нет. Потому, что блок памяти (какой угодно памяти, которая была в 60-х годах или сейчас) всё равно имеет какое-то время цикла своей работы. Раньше, чем этот цикл не закончится, следующее обращение к нему подать нельзя. Стало быть, следующая команда должна быть в следующем блоке. И тогда со скоростью прибавления единички мы будем запускать один за другим блоки и, естественно, через какое-то время с такой же разницей во времени будут идти команды на обработку в дальнейших устройствах. Поэтому в БЭСМ-6 было 8 блоков (нумерация с 0 до 7). Сразу привыкнем, что все адреса в восьмеричной системе счисления. Конечно, чем больше степень параллелизма (или интерливинга — расслоение памяти), то, вообще говоря, в процессе работы обращения по разным направлениям за взятием операндов, запись результатов, команд, внешними обменами, они довольно заметно будут использовать (я не говорю 100%) эту возможность параллелизма просто из-за равномерности. Эта идея реализована во всех машинах начиная с 70-х годов и по сегодняшний день. Конечно, в современных машинах эта степень уже не 8 и даже уже не 16, а 32, 64 и т.д. Тогда сколько вы там потребностей обращения в память не имели, они, как правило, будут выполняться параллельно.

Вот — это первое вспомогательное решение параллелизма работы блоков памяти вот с таким распределением адресов: каждые следующие по адресу данные находятся в следующем блоке памяти по сравнению с данными с предыдущим адресом.

Кстати, память бывает двух типов, оба на букву «а». Сейчас мы с вами рассматриваем наиболее часто используемый тип — *адресная* память, где чтобы найти нужное, надо указать место в памяти. А есть, так называемая, *ассоциативная* память, когда вы находите по некоему признаку. Это означает, что в полном случае нужно осуществить перебор.

Теперь, команды будут поступать на УУ. Операции реализует АЛУ. Поскольку операции бывают разной длины по времени выполнения в АЛУ, соответственно, в работе УУ, которое передаёт туда операции, могут быть задержки по причине того, что там выполняется какая-то длительная команда. И поток команд из ОП нужно где-то сохранять. Для этих целей был организован буфер на 4 слова, назывался он *буферные регистры слов* (БРС). На самом деле это буфер команд. В каждом слове было 2 команды, итого, здесь было 8 команд. Т.е. если есть какая-то задержка, то буфер заполняется. Если совсем полностью заполнится, то совсем приостановится выдача новых адресов и считывание новых команд. Всё это, конечно, синхронизовано. Так или иначе, в БРС всё задержится, а когда УУ освободится, команды будут готовы. Этот буфер естественен, как буфер, который позволяет в случае задержки прохождения данных через УУ, которые возникают по многим причинам, по завершении сразу иметь команду для дальнейшего выполнения.

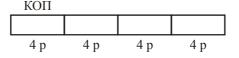

Прежде, чем этот буфер до конца (его функцию) рассмотреть, давайте посмотрим, что же за команды были в машине БЭСМ-6.

Команды были такие:

| - 4 - | - 8 - | - 12 - |  |

|-------|-------|--------|--|

| ИР    | КОП   | A      |  |

КОП — код операции (какую выбрать операцию), А — адрес и ИР — индексный регистр. Индексный регистр (ИР) нужен для того, чтобы избавиться от переменных команд. Как ситуация выглядела раньше? Пусть некоторая команда работает с массивом данных. Чтобы работать со следующим элементом массива нужно прибавить «1» к адресу, т.е. бралась сама команда из памяти, к ней прибавлялась «1» и записывалась на тоже место. Если цикл, то надо изменять все команды в цикле. Таким образом, цикл увеличивался в 2 раза. Это и по времени, ведь надо считать, записать и т.д. Нужно было сделать так, чтобы эти команды не менялись. А как брать следующие данные из массива данных? Очень просто: ИР заполнять информацией, и тогда истинный исполнительный адрес будет вычисляться следующим образом:

$$A_{\text{ИСП}} = \langle \text{ИР} \rangle + \text{A}$$

Таким образом, в конце цикла достаточно изменить ИР, иногда даже совмещается с командой перехода на продолжение цикла. В частности, в БЭСМ-6 такая команда и была. Она называлась КЦ (конец цикла). Эта команда проверяла значение ИР, и если он был не нуль, то она изменяла его значение (от положительной величины отнимала единичку, к отрицательной — прибавляла) и уходила на новый виток цикла.

Итак, в УУ были 15 ИР по 15 разрядов. Хватает? 15 вложенных циклов — вполне хватает, тем более в 60-е годы оборудование приходилось экономить. Поэтому 4 разряда вполне хватает, чтобы их (от 1 до 15) адресовать (0 — без индексации).

Хорошо. Сколько нужно под код операции (КОП)? 8 разрядов. Что такое 8 разрядов — это 256 кодов операций. Конечно же, столько не набиралось, но 7 разрядов не хватало.

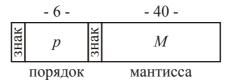

В 60-е годы блоки памяти работали с циклом 2 мкс, среднее время выполнения операции в АЛУ — 1 мкс. Дальше совершенствовалась и ускорялась работа памяти и АЛУ, но память отставала от скорости выполнения операции. И вот такая приемлемая по скорости работы память была в промышленности доступна в несколько тысяч ячеек всего. И вот на машине БЭСМ-6 слово было 48 разрядов, чтобы в него можно было поместить число с плавающей запятой, где под порядок отводится какая-то величина и под мантиссу тоже:

где мантисса  $(0 \le M < 1)$  — 40 разрядов, под порядок (p) — 6 разрядов. Итого: 6 + 40 + 2 = 48 разрядов в слове позволяли получить достаточную точность  $(2^{-40})$ . А какой порядок? 6 разрядов, поэтому  $2^{\pm 64}$ . Поэтому диапазон достаточно большой, точность достаточно хорошая. В других машинах какие-то другие колебания, но в принципе вот это вот положение, где-то было 7 разрядов порядок, 8, 10 (это  $2^{\pm 1024}$ ). Разрядность где-то увеличивалась, но бывало, и уменьшалась. Если взять машину 32-х разрядную (это была целая эпоха 32-х разрядных машин), то там точность немножечко поменьше. Для каких-то вычислений этого было достаточно, для каких-то — нет. И тогда в некоторых машинах были задействованы операции с удвоенной точностью. Т.е. у вас операция делалась не с 24-х разрядными, а с 48-разрядными. Помещалось 2 слова, ну и т.д. (первую половину в несколько байт, и вторую — байтная адресация). В некоторых случаях операции с удвоенной точностью не делали, а делали программно (в частности программы для любой машины сделаны с любой точностью).

Раз уж мы так говорим, давайте напишем общую формулу:

$$X = \pm 2^{\pm p} \cdot M$$

где p — целое,  $0 \le M < 1$ . Иногда бывает нормализованная мантисса, это когда для положительной мантиссы «1» в старшем разряде. Тогда  $\frac{1}{2} \le M < 1$ .

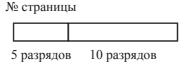

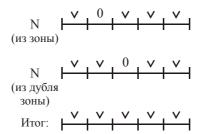

Повторяю, само количество данных в памяти было не велико — 4 килослова (в переводе на байты:  $6 \times 8 = 48$  — в слове 6 байт). Где-то впереди — память 32 килослова. Сколько нужно разрядов при адресации словной, чтобы адресовать 32 килослова. Нужно 15 разрядов. Таким образом 8 + 4 = 12 да 15, получается 27 — ни два, ни полтора. Поэтому поместить одну команду в слове — это преступление. И решили, пусть здесь адрес будет 12 разрядов, а индексный регистр пусть будет 15-ти разрядный. Таким образом, вы складываете содержимое некоего указанного индексного регистра (он, естественно, 15-ти разрядный), и к нему прибавляется некая величина 12-ти разрядная, итоговый адрес получается 15-ти разрядный. Таким образом, появилась первая структура команд, которая даёт в сумме 24 разряда, и таким образом, в каждом слове появляется по 2 команды:

Понадобилось всё-таки иметь для некоторых команд полный адрес. И появилась вторая архитектура команд, которая выглядела следующим образом:

| -45- |     | - 15 - |  |

|------|-----|--------|--|

| ИР   | КОП | A      |  |

Индексный регистр (ИР) — 4-х разрядный, код операции (КОП) уменьшился до 5 разрядов, адресная часть — 15 разрядов. Ясно, что одну структуру от другой отличают значения старшего разряда КОП.

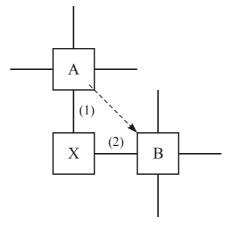

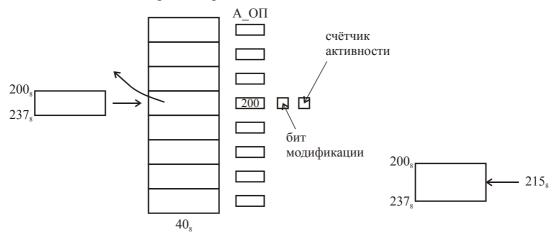

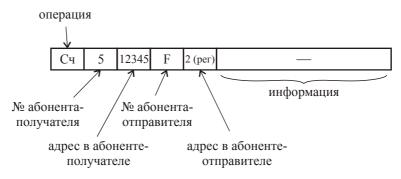

Таким образом, в УУ (см. Рис. 1) поступала команда на, так называемый, регистр команд (РК), где ИР, КОП и адрес (А). В УУ существовал сумматор адреса (СмА), где выполнялось вычисление исполнительного адреса. Сюда поступал адрес, по номеру ИР выбиралось содержимое ИР, и передавалось на СмА. Здесь происходило сложение, и на регистр результата (РР) поступал КОП и адрес исполнительный (А<sub>ИСП</sub>). Вот такая работа УУ.

Как вы сами понимаете, некоторые операции при такой структуре здесь могли выполняться целиком до конца, не требуя задействования АЛУ. Например, операция передачи содержимого адресной части (A) в индексный регистр (ИР), операция сложения индексных регистров. Итак, выход здесь — адрес исполнительный ( $A_{\rm ИСП}$ ). Что  $A_{\rm ИСП}$  нам даёт? Если это адрес операнда, то его можно подать в ОП, и (не сразу, т.к. блок ОП может быть занят) хотя бы через микросекунду данные должны пойти в сторону АЛУ. Но блок может быть занят. Может возникнуть такая ситуация, когда мы и это делаем, и записываем что-то, и работаем с внешними устройствами (ВУ), тогда придётся подождать, и это будет уже дольше.

Для того чтобы операция в АЛУ встретила готовый результат, был поставлен некий буфер из 4-х ячеек, причём тогда не было интегральных схем, а были навесные элементы. Этот буфер назывался *буферный регистр чисел* (БРЧ). Когда запускался блок памяти (и если он запускался), этот регистр всегда должен быть свободен для приёма числа. На это требуется время, и мы договорились, что время может быть и заметным. Стало быть, готовую операцию, если АЛУ готово, подавать нельзя. Это бессмысленно: оно будет ждать, а мы хотим, чтобы не ждало, чтобы АЛУ работало непрерывно. Что нужно сделать? Ставился ещё один буфер, и вот эта операция попадала в этот буфер, одновременно с подачей адреса в память. Он назывался *буфер арифметических команд* (БАК). И вот этот буфер был на четыре команды вот таких вот: КОП и номер БРЧ. Таким образом, сюда приходили КОП и номер БРЧ, который зарезервирован для приёма операнда из памяти по адресу А<sub>ИСП</sub>. Всё, эта команда попала в БАК. Впереди неё находятся ещё 3. Т.е. пока данные перейдут из памяти, эта команда постепенно подойдёт к АЛУ (на самом деле, никакого движения не было, просто переназначались регистры). И когда уже все эти операции выполнятся, и наша подойдёт к АЛУ, данные по адресу А<sub>ИСП</sub> будут считаны из памяти практически всегда, т.е. они будут готовы к

использованию. Можно сказать, что данные из памяти считались раньше, ну значит, эти данные будут ждать своей команды. АЛУ простаивать будет очень редко. Коэффициент полезного действия арифметико-логического устройства (АЛУ) БЭСМ-6 был порядка 80%. Не 100, но достаточно хороший коэффициент загрузки арифметико-логического устройства, оно работало 80% времени. Были какие-то моменты простоя.

Итак, за счёт БАК и БРЧ мы обеспечили параллельную работу оперативной памяти и арифметико-логического устройства. Если команда является не командой, подлежащей выполнению в АЛУ, а команда передачи управления, т.е. перехода на новую последовательность выполнения команд, то тогда этот адрес должен передаваться на *счётчик адреса* (СчАдр), и начнётся новая выборка. Всё, что набрали в БАК и БРЧ будет не нужно, и естественно будет задержка.

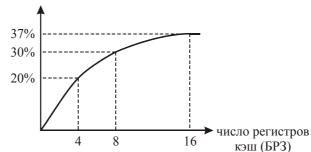

Раз так, то возникла идея: а что если (и это была одна из первых реализацией cache) сделать так, что если этот адрес того командного слова в памяти, которое, может быть, уже есть в БРС, т.е. если у вас есть короткий цикл, укладывающийся в 8 команд, а циклы задач линейной алгебры все такие, то можно сделать так: поставить 4 маленьких регистра (15 разрядов) и назвать их *буферные регистры адресов слов* (БАС), которые находятся в БРС (когда вы из памяти берёте слово в БРС, то в БАС помещаете его адрес, по которому взяли из памяти). И когда возникает код операции передачи управления, этот адрес сравнивается со всеми адресами в БАС — работает полностью ассоциативный сасhе. Если совпал, то тогда мы назначаем взятие отсюда. Время работы регистров во всех наших рассуждениях будем условно считать равным нулю по сравнению со временем работы памяти. Т.е. если у вас цикл в пределах 8-ми команд, вам никогда не будет нужно обращаться в память.

Моделирование показало, что на задачах линейной алгебры выигрыш получается 10-12% производительности по времени выполнения задач — это огромный выигрыш. Машина БЭСМ выполняла миллион операций в секунду в то время, когда предыдущие машины были порядка 100 тысяч операций в секунду, так это целая машина.

Т.е. возник кэш команд. Слова такого и не знали, так что их не было, но, как видите, сделали.

Между прочим у Лебедева в докладе «Пути развития советского математического машиностроения» он рассказывал про машину БЭСМ (БЭСМ-1 не называл, просто — БЭСМ), он тогда и эти вещи, и параллелизм, т.е. идеи машин 2-го поколения и 3-го, в этом докладе анонсировал.

Итак, всё вроде бы хорошо, циклы мы держим в БРС, не умещается, ну... Конечно, хорошо бы в этом случае иметь больше, указатель на более объёмное оборудование — нужен компромисс.

Очень интересный был момент: перед БЭСМ-6 практически в том же году была закончена работа над машиной «Весна». Главный конструктор — Владимир Константинович Левин, академик. Машина делалась в Минске. Систему команд делали так: ИПМ-овские «мудрецы», естественно прекрасные математики, говорят: «хорошо бы вот такую операцию ещё» — инженеры говорят: «будет сделано» — «а хорошо бы сделать вот таких операций» (для шифровки/дешифровки) — инженеры говорят: «будет сделано». И когда машина была сделана, в Минск приехали математики из ИПМ — огромный зал... множество стоек... — что это такое? Понимаете, должен быть разумный компромисс между аппаратурой и логической компонентой вычислительных машин (набором системы команд, программами и т.д.).

Итак, вот этих буферов хватает, если не делать запись результатов. Команды в случае циклов сидят в БРС, выборка операндов происходит даже раньше, чем приходит команда, АЛУ работает 80%. А почему? Знаменитая проблема: условный переход.

Вот идёт последовательность команд, а дальше команда условного перехода: либо сюда, либо туда, в зависимости от условия, например, положительным или отрицательным является результат предшествующей операции, пусто/не пусто после операции, положительный или отрицательный порядок, разные условия могут быть для выполнения этой проверяющей операции. Но команда предшествующая должна выполниться. И наша операция условного перехода, проходя здесь, не даёт возможности следующей операции поместить в БРС. Вот почему во многих машинах делается так: как только УУ поймало команду условного перехода, сразу начинают выбираться обе последовательности команд, чтобы они были готовы. Какая-то не понадобится, ну и чёрт с ней, зато готовая будет команда. В БЭСМ-6 такой роскоши не было, поэтому АЛУ сколько-то да простаивало. Вот это основной вклад в эти 20% простоя АЛУ.

Были и другие вещи, связанные с этим. Тогда, конечно, никто не говорил слова CISC (completed instruction set command). Вот когда сделали RISC (reduce instruction set command), тогда сказали: «А это что у нас было? Ах, CISC было...», тогда появилось это, а до этого не говорили. Вот в этом полном наборе операций существовали команды косвенной адресации, да ещё и многоярусные. Что это означает? Вот у вас есть операции:

| ИР2 | косвенная<br>адресация | $A_2$          |

|-----|------------------------|----------------|

| ИР, | КОП                    | $\mathbf{A}_1$ |

Что делается? Адрес искался следующим образом: находился исполнительный адрес первой команды, фактически указывался адрес ячейки, из этой ячейки бралось 15 младших разрядов, и складывались так:

$$(\langle \text{UP}_2 \rangle + \text{A}_2) + \langle \text{UP}_1 \rangle + \text{A}_1$$

Т.е. у вас адрес был не прямой, а адрес получился косвенный. Вы указали адрес ячейки, в которой находится адрес вашего операнда. Сами понимаете, что можно использовать как «дом, который построил Джек»: адрес ячейки, в которой адрес ячейки, в которой адрес ячейки в которой находится операнд. Трансляторщики схватились за это урча и просто в восхищении, и программы запестрили вот этими командами. Больше того, транслятор в своей работе стал их использовать, оттранслированный код стал появляться с такими операциями. А что происходит: прежде чем получить  $(\!\langle \mathrm{HP}_2 \rangle + \mathrm{A}_2 )$ , её же надо считать из памяти (15 разрядов), значит нужно здесь задержать. А для этого нужно время. И вот вам второй компонент этих 20%.

Самое страшное: что делать с записью результата. Давайте запишем: «запись в ячейку  $\alpha$  и считывание из ячейки  $\alpha$ »:

3π α Сч α

Можно так написать? Можно. Так или иначе, есть команда, которая сейчас будет записывать в ячейку  $\alpha$ , а сразу за ней пошла команда, которая считывает из  $\alpha$ , а так как считывание операнда из памяти происходит раньше попадания команды в АЛУ, то вторая команда получит старое значение. И вся наша параллельность к чертям из-за одной команды записи. Что же нужно делать?

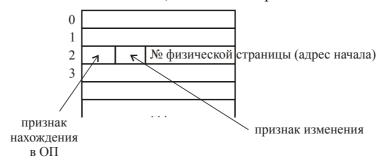

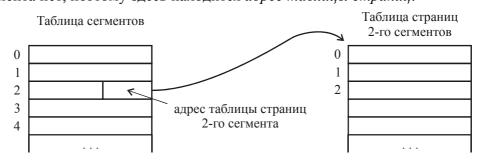

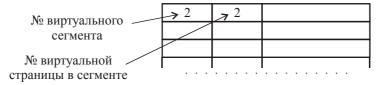

А нужно делать вот что: результат будет записываться в некий буфер, реально в БЭСМ-6 было 8 ячеек (см. Рис. 1). Они были названы *буфер записанных результатов* (БР3) и к тому же был здесь *буфер адресов записанных результатов* (БА3). И это получился второй кэш полностью ассоциативный.

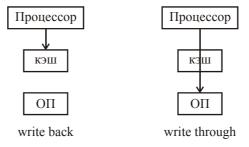

Так вот, очень просто. Когда приходила команда записи, для неё всегда была одна свободная позиция. Так делалось, потому что самая старая выкидывалась в память. И тогда  $A_{\rm ИСП}$ , вообще говоря, сравнивался со всеми адресами в БАЗ, потому что, может быть, уже только что недавно записывали. Если нет, то всегда идёт в БРЗ, там всегда есть свободная позиция. Как только команда попадала в УУ, то в БАК помещался соответствующий номер БРЗ. Итак, в БАК попадали КОП и номер БРЧ или БРЗ. Да, можно было сделать его общим и для чтения и для записи, но было сделано так. Когда мы придём к теме кэша, мы этот вопрос ещё подымем. Моделирование показало, что при такой организации выигрыш приличный (до 30%).

Вот, собственно говоря, это всё, кроме одного: как же определяется старшинство? Оно определяется очень интересно. Рисуем игровую таблицу:

|   | 1 | 2 | 3 | 4 |

|---|---|---|---|---|

| 1 |   |   | 1 |   |

| 2 |   |   | 1 |   |

| 3 | 0 | 0 |   | 0 |

| 4 |   |   | 1 |   |

Допустим, что пишется в 3-й регистр. Тогда он делается самым молодым (по горизонтали ставим «0»). Против него (по вертикали) ставим «1». Кто набирает все «1» (в строке), тот выкидывается. И при этом это обмоложение происходит при любом совпадении, будь то по записи (если не нашло, то свободная становится самой молодой), по считыванию (пришло считывание, и тот регистр, из которого будут браться данные для операции, когда она подойдёт, делается самым молодым — раз данные нужны, значит, скорее всего, понадобятся ещё).

Таким образом, у нас полностью завершена структурная схема машины, и всё в ней работает, обеспечивая максимальную загрузку АЛУ. Как сами понимаете, при формульном счёте мы тоже не лезем за операндами в память (берём из БРЗ). За счёт устройств промежуточного хранения информации активных и неактивных удалось организовать параллельную работу основных устройств: оперативной памяти, устройства управления и арифметикологического устройства (в первую очередь для обеспечения полной загрузки).

Вы знаете, дело в том, что приходили сведения, что вот Motorola сделала процессор такой-то. Господи, почему же они так сделали? (как бы становясь в позицию игры Бендера с васюкинцами: «Что мне делать?» — «Сдавайся...»). На самом деле всё очень просто: они в чём-то ошиблись, и им надо было переделать всё. Переделать — это значит задержать по времени выпуск процессора, выпуск машины и т.д. Они сделали заплату. И вот этот весь такой ... самое совершенное, что только можно придумать! А оказывается, что это не совершенное, это просто вынужденная заплата, и вовсе антисовершенное решение. А здесь всё чётко предельно ясно. Когда появилась машина Стау (другой уровень параллелизма, а именно уровень параллелизма исполнения самих операций), Лев Николаевич сказал: «Батюшки! Да это ж БЭСМ-6!» Конечно, ничего похожего нет, но ясность и чёткость структуры позволили ему это сказать. Вот смотрите, что мы здесь имеем? Здесь имеем, конечно, ярко выраженный конвейер команд, который Сергей Алексеевич называл «водопроводом»: где-то задержка, другое не течёт, когда клапан открыли, кранчик открыли, всё потекло дальше. Это называется «конвейер» или «магистраль» для команд. Вот смотрите: одна команда выполняется, четыре стоят в очереди, это здесь обрабатывается, здесь какие-то выбираются. Реализован полностью довольно активно конвейер команд. Это выполнение команд на разных стадиях: эта здесь, эта здесь, эта вот здесь. Ну а конвейер внутри операции (параллелизм операций) мы рассмотрим позднее (это машина Cray).

Был задан вопрос относительно этих самых злосчастных условных переходов. Об этом, правда, уже говорилось, что выбираются из памяти оба потока команд: и те, которые идут после условного перехода, и та ветвь, на которую указывает условный переход. Но для этого действительно нужно анализировать этот условный переход сразу, как только выбирается команда. Помните, мы смотрели как пример машину БЭСМ-6: команды поступают в буфер. Так вот на входе буфера, ещё задолго до того, как она попадёт в устройство управления и начнёт дешифрироваться, и выясниться, что это команда условного перехода, нужно обнаруживать команду условного перехода, т.е. производить предварительную дешифрацию. Но это ведь сложно, потому что ведь нужно знать исполнительный адрес команды, а перед этой командой могут быть команды изменения индексных регистров. Вот такой предварительный достаточно сложный анализ в современных процессорах действует, по-разному. По разным причинам может производиться сложный предварительный анализ, прежде чем запустить команду уже в полное исполнение. Так что это очень не простая вещь. Условный переход — это головная боль для разработчиков. Но вопрос был задан на эту тему, так что ещё раз этот момент подчеркнём.

Теперь, чтобы закончить с параллелизмом основных устройств машины, давайте посмотрим, а какой эффект вносит вот этот структурный параллелизм, который мы рассматривали.

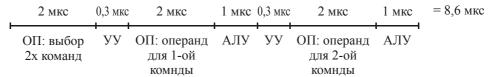

Пусть работает некая машина, которая имеет несколько физических параметров, т.е. время работы блоков памяти, время выполнения операций алгоритмов на логическом устройстве, сколько времени работает УУ, но нет никакого параллелизма.

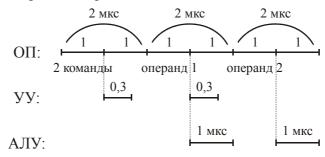

2 мкс (такое тогда было время) работал блок памяти. За это время выбирается одно слово, содержащее 2 команды. Затем у нас работает устройство управления, которое работает 0,3 мкс, образуя исполнительный адрес команды, которая требует считывание операндов из памяти. Затем, когда выяснилось, что нужно считывать операнд (перебираем какойнибудь массив, понятно, что он не поместится в кэш, хотя в этом случае кэша не будет, поскольку нет никаких буферов). Итак, 2 мкс тратится на считывание операнда для первой команды. Затем выполнение операции — работает АЛУ — 1 мкс, поскольку БЭСМ считала 1 миллион операций в секунду, что значит 1 MIPS. Не 1 Мфлопс, а 1 MIPS. Что касается Мфлопс, то было 0,3 Мфлопс, поскольку всегда при выполнении разных счётных вычислительных задач, количество операций +, -, ×, ÷ составляет приблизительно 30% от общего числа операций (статистика такая по Вычислительному центру:  $\pm - 16\%$ ,  $\times - 15\%$ ,  $\div -$ 1-2%, всё остальное — обслуживающие операции). В среднем команда выполняется за 1 мкс. Итак, мы закончили выполнение одной команды, у нас уже готова вторая команды. Мы её обрабатываем в устройстве управления, снова надо брать операнд (операнд для второй команды), и, собственно, выполнение операции в АЛУ. Теперь всё складываем: 8,6 мкс. В машине, которая учитывает параллелизм, это будет 2 мкс, но поскольку КПД 80%, значит, будет немного больше, чем 2 мкс. В любом случае, соотношение примерно 4: 1 только за счёт структурного параллелизма.

Давайте чуть-чуть поиграемся вот в каком варианте: я буду с памятью параллелить работу УУ и АЛУ, саму память параллелить не буду. Дело в том, что, вообще говоря, цикл памяти даже и сейчас в интегральных схемах имеет 2 части. Если мы имеем в виду считывание операнда, сам операнд появляется при запуске некоторых блоков памяти, где нужно взять этот операнд, несколько раньше, чем заканчивается цикл. Вот память на магнитных сердечниках (маленькие ферритовые колечки, диаметром порядка десятых долей миллиметров, через которые проходили провода для записи, для считывания, для регенерации) — за 1 мкс происходило считывание командного слова. При этом разрушалось состояние намагниченности сердечников, и с некоторого промежуточного регистра он снова записывался, на что требовалась ещё 1 мкс. Короче говоря, через 1 мкс появлялись 2 команды. Можно было запускать УУ. Вот оно начало свой цикл 0,3 мкс. И дальше оно уже знает, где нужно брать операнд. Но так как память у нас не запараллелена, то мы ждём. Запускаем цикл считывания операнда. Но операнд приходит быстрее — за 1 мкс. Раз он пришёл, мы можем начать работу АЛУ. Таким образом, следующая команда у нас есть, и можно было бы её запустить параллельно после выбора первого операнда.

Но всё равно понадобится второй операнд. Что у нас получилось? Я запараллелил работу памяти, но внутри памяти не запараллелил работу отдельных блоков, а также УУ и АЛУ. Я получил 6 мкс. Грубо говоря, здесь 3 : 1. Здесь всё-таки ясно, что нужно обязательно иметь интерливинг памяти и устройства промежуточного хранения информации между основными устройствами. Вот какое значение имеет структурный параллелизм.

На счёт феррита вспоминается 2 интересных случая. Приезжали к нам американцы, ну и в Институте точной механики и вычислительной техники им показывали ферритовые сердечники. Американцы ходили, смотрели: «Да, очень интересно!» И рукой незаметно облокачивались, рука жирная — сердечники прилипали, и так незаметно в карманчик. Кстати, наши тоже самое делали, когда к ним ездили. Понимаете в чём дело, психологический момент здесь тоже важен.

Вот ещё один такой случай. Дело было в государственном масштабе. Мы с вами в скорости будем рассматривать машину Эльбрус-2. В MIPS, учитывая многопроцессорность, её производительность порядка 100 миллионов операций в секунду (100 MIPS). И вот, эта машина планировалась в дальнейшем, но ещё далеко было до отработки полностью структурной схемы. Так вот в печати (сначала в «Московской правде», потом в «Правде») было написано, что уже поставлено на поточное производство. Т.е. ну чистейший обман! Сначала были «термины Бурцева», потом статья в «Правде». Это было сделано совершенно сознательно. В конечном счете, машина появилась, но далеко не в то время, когда было объявлено. Ну и другие подобного рода были дезинформации. Они привели к тому, что действительно американцы как-то ощутили, что хорошая разработка, значит будут иметь русские (Советский Союз) машины. Раз будут иметь машины, значит всё: и расчёт ядерных вещей, бомбы, самолёты, ракеты. И это привело к определённому соглашению в области вооруженных сил. Американцы огромный доклад представили правительству и президенту на предмет срочного выделения огромного количества средств на дальнейшее развитее вычислительных систем в интересах конкурентной способности и безопасности Америки. Т.е. это всё было не случайным. Это сознательное было решение высших инстанций поместить вот такую существенно опережающую на несколько лет информацию.

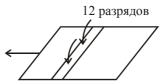

Итак, мы с вами рассмотрели параллелизм работы, а сейчас попытались его ярко себе представить «что было, если бы не было». Получается так: память запараллелена, осталось запараллелить два других основных устройства машины, т.е. арифметико-логическое устройство и устройство управления. Первая часть получилась, прежде, конечно, столько, сколько нужно увеличилась параллельность работы блоков памяти. Распараллелим АЛУ потребуется больше операндов в единицу времени, больший поток записывания результатов. Поэтому, конечно, это тоже будет с этим сопрягаться. Главное, что усилия пошли на распараллеливание работы арифметико-логического устройства. Что касается устройства управления — это очень сложно распараллелить. Только что мы с вами говорили об условном переходе, что команды условного перехода можно как-то ловить, но не всё так просто. Т.е. распараллелить работу УУ очень сложно, разве что сделать несколько (увеличение объёма аппаратуры — само собой, но миниатюризировались схемы, дешевели, и увеличение объёма стало вполне разумным). Можно взять несколько ветвей программы, если быть уверенными, что они независимы (выполняются над независимыми данными) и запустить на разных УУ. Но это не так активно в мире развивалось, и мы это не будем затрагивать. А вот АЛУ напрашивалось его распараллелить.

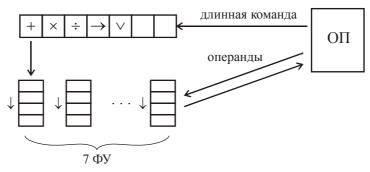

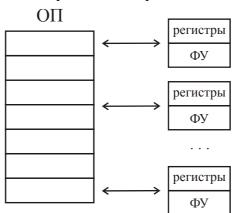

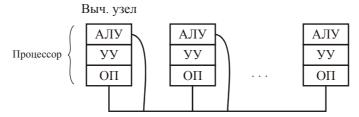

#### Параллелизм работы АЛУ

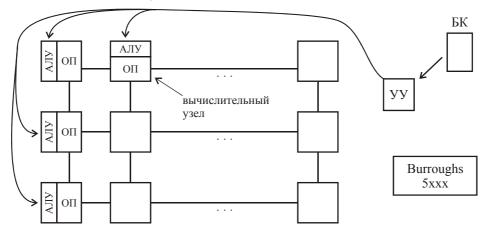

Распараллеливание АЛУ напрашивалось по двум направлениям. Первое — разбить его на несколько функциональных устройств (ФУ). Тогда и появилось название «функциональные устройства», т.е. выполняющие отдельные функции или операции, отдельные операции и группы операций. Например, устройство «сложитель/вычитатель» (понятно, что это родственные операции полностью), устройство «умножитель», устройство «делитель», устройства

логических операций (конъюнкция, дизъюнкция). Универсальное арифметико-логическое устройство, где схемы позволяли выполнять много разных операций, развели.

Каждое устройство стало попроще, но эти устройства можно запустить параллельно, если операции на них будут выполняться с независимыми данными. Если у вас выполняется операция сложения и получается результат, и он используется в следующей операции умножения, то, конечно, следующая операция выполняться не может до тех пор, пока не закончится операция сложения. А если операция умножения работает с данными, не связанными с результатом предыдущей операции сложения, то пожалуйста — очень хорошо.

И вот появилось разделение на отдельные функциональные устройства. Итак, АЛУ разбивается на отдельные функциональные устройства (ФУ).

Этот шаг постепенно прививался в разработке вычислительных машин. В начале 70-х годов активно пошла серия машин CDC 6xxx (Control Data Corporation). И уже в старших моделях этого ряда стало это введение появляться: стал выделяться сложитель/вычитатель, умножитель и делитель.

Ещё раз про фирму Control Data Corporation (CDC): мы говорили и о том, что в Советском Союзе организацией, которая разрабатывала самые высокопроизводительные машины, был Институт точной механики и вычислительной техники. В Америке тоже: фирма IBM — это была фирма, производящая огромное количество машин на весь мир, но были и фирмыгранты. Самый грант был Control Data Corporation. И не удивительно, главный конструктор этой фирмы был Сеймур Крэй до того момента, пока он сам не выделился и организовал фирму Cray Research, и в 1976 году вышла машина Сгау-1. С этого момента началась эра суперкомпьютеров (появилось это название). На самом деле, эта машина позволяла осуществлять при двух конвейерах существенно больше, чем 100 миллионов операций в секунду (машина CDC 6000 — всего несколько миллионов операций в секунду) во многом за счёт вот этого параллелизма: разбиения на многие функциональные устройства. Считается, что именно машина Сгау и олицетворила, полностью реализовывала подход разбиения на множество функциональных устройств, объединяемых в различные группы — это был первый шаг. И второй: была достигнута конвейерность выполнения операций в каждом из этих функциональных устройств.

Если мы будем рисовать схему, будем говорить о некоем вертикальном параллелизме, а именно параллелизме работы ФУ, и горизонтальном параллелизме выполнения операций в каждом из этих устройств в конвейерном режиме. Всё это дало весьма большой выигрыш производительности. Это следующий этап развития параллелизма — параллелизм выполнения операций. На БЭСМ-6 мы с вами отметили в конце нашего рассмотрения активно реализованный конвейер команд, то здесь мы с вами увидим конвейеры (их много) в самих функциональных устройствах. Так что такие гранты были. Ещё к грантам можно отнести машины фирмы Boroughs. А рабочими лошадками были фирмы IBM, DEC (Digital Equipment Corporation), целый ряд других фирм. Таких машин выпускалось не так много, но они все были самой высокой производительности.

Второе, о чём будет разговор — это о конвейере. Сейчас эти компоненты с вами проговариваем, а потом посмотрим саму структурную схему машины Стау, увидим там достоинства и недостатки, и посмотрим, каковы же были решения, преодолевающие эти недостатки.

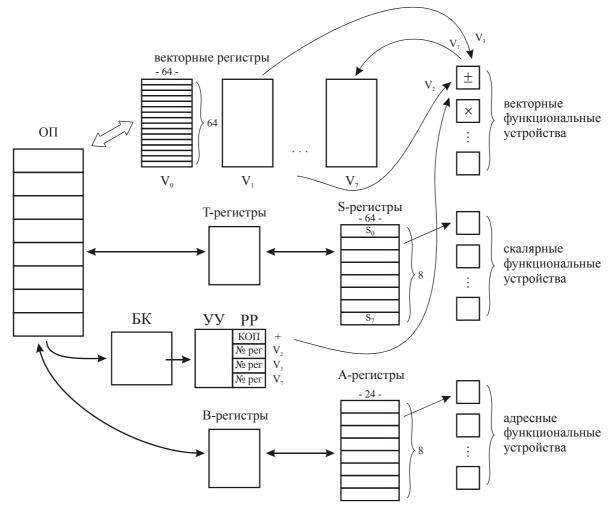

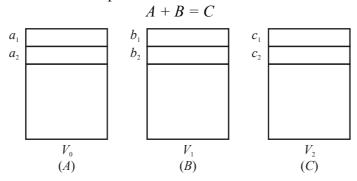

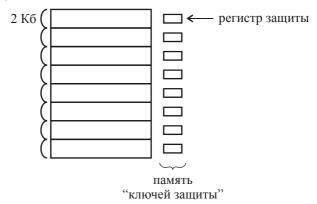

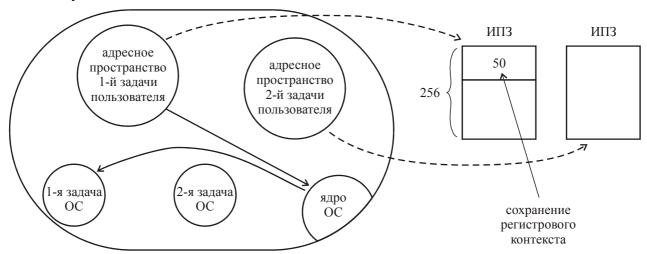

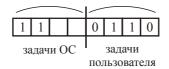

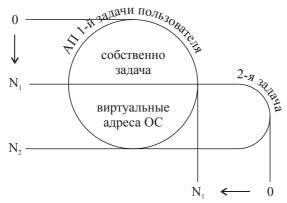

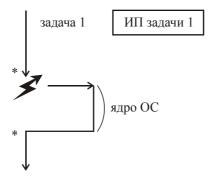

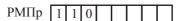

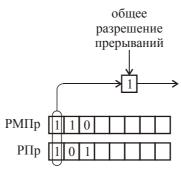

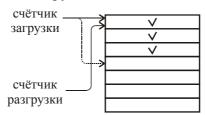

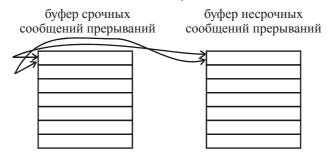

Ученики и последователи Сеймура Крэя, которые остались в фирме Control Data Corporation, сделали машину Cyber 205. И вот очень долго в мировой литературе в самых разных журналах активно обсуждалось, для каких задач удобен Cray, для каких задач удобен Cyber